发布时间:2025-02-15 18:35:11 点击量:

HASH GAME - Online Skill Game GET 300

比特币是一种p2p(peer-to-peer)形式的虚拟加密数字货币,其概念最初由中本聪在2008年11月1日提出,并于2009年1月3日正式诞生。比特币的独特之处在于,它不依靠特定货币机构发行,而是依据特定算法通过大量运算来产生。比特币交易使用整个p2p网络中众多节点构成的分布式数据库来确认并记录所有的交易行为,并使用密码学设计来确保安全性。从密码学的角度而言,比特币是基于sha-256哈希算法的工作量证明pow(proofofwork),其交易完整性取决于sha-256的碰撞性和前映像阻力。哈希算法是一种将可变长度的数据作为输入并产生固定长度的哈希值作为输出的算法,其本质是对信息的提炼。自1993年以来,美国标准与技术研究所先后设计并发布了多个版本的安全哈希算法sha(securehashalgorithm),sha-256正是其中一种哈希长度为256位的安全哈希算法。

使用矿机来进行比特币挖矿的核心是根据矿机计算sha-256的运算能力来获得奖励。对于矿机而言,芯片尺寸、芯片运行速度和芯片功耗是决定矿机性能的至关重要的三个因素,其中,芯片尺寸决定芯片成本,芯片运行的速度决定矿机运行速度,即算力,芯片功耗决定耗电程度,即挖矿成本。在实际应用中,衡量矿机最为重要的性能指标是单位算力所消耗的功耗,即功耗算力比。为了提高安全性,在比特币协议中,要进行两次sha-256。因此,对于比特币矿机而言,最重要的就是以较低的功耗算力比来实现哈希算法sha-256。

根据本公开的第一方面,提供了一种用于执行哈希算法的电路,包括:输入模块,被配置为接收数据;以及运算模块,被配置为基于接收到的数据计算哈希值,运算模块包括:以流水线结构布置的多个运算级,多个运算级中的每个运算级包括第0扩展寄存器至第15扩展寄存器,每个扩展寄存器被配置为存储当前运算级的扩展数据;以及多个扩展数据运算逻辑模块,每个扩展数据运算逻辑模块设置在多个运算级中的相应的相邻两个运算级之间,相邻两个运算级包括第一运算级和在第一运算级之后的第二运算级,每个扩展数据运算逻辑模块包括:第一子模块,被配置为基于第一运算级的第2扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第0扩展寄存器中的扩展数据;第二子模块,被配置为基于第一运算级的第0扩展寄存器和第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;第三子模块,被配置为基于第一运算级的第3扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第1扩展寄存器中的扩展数据;以及第四子模块,被配置为基于第一运算级的第1扩展寄存器和第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;其中,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据是第一运算级的第i扩展寄存器中存储的扩展数据,其中4≤i≤15且i为整数。

根据本公开的第二方面,提供了一种用于执行哈希算法的电路,包括:输入模块,被配置为接收数据;以及运算模块,被配置为基于接收到的数据计算哈希值,运算模块包括:以流水线结构布置的多个运算级,多个运算级中的每个运算级包括第0扩展寄存器至第15扩展寄存器以及第一附加寄存器和第二附加寄存器,每个扩展寄存器被配置为存储当前运算级的扩展数据,每个附加寄存器被配置为存储用于计算扩展数据的中间数据;以及多个扩展数据运算逻辑模块,每个扩展数据运算逻辑模块设置在多个运算级中的相应的相邻两个运算级之间,相邻两个运算级包括第一运算级和在第一运算级之后的第二运算级,每个扩展数据运算逻辑模块包括:第一子模块,被配置为基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第一附加寄存器中的中间数据;第二子模块,被配置为基于第一运算级的第一附加寄存器中存储的中间数据和第一运算级的第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;第三子模块,被配置为基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第二附加寄存器中的中间数据;以及第四子模块,被配置为基于第一运算级的第二附加寄存器中存储的中间数据和第一运算级的第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;其中,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据是第一运算级的第i扩展寄存器中存储的扩展数据,其中2≤i≤15且i为整数。

根据本公开的第三方面,提供了一种用于执行哈希算法的电路,包括:输入模块,被配置为接收数据;以及运算模块,被配置为基于接收到的数据计算哈希值,运算模块包括:以流水线结构布置的多个运算级,多个运算级中的每个运算级包括第0扩展寄存器至第15扩展寄存器以及第二附加寄存器,每个扩展寄存器被配置为存储当前运算级的扩展数据,第二附加寄存器被配置为存储用于计算扩展数据的中间数据;以及多个扩展数据运算逻辑模块,每个扩展数据运算逻辑模块设置在多个运算级中的相应的相邻两个运算级之间,相邻两个运算级包括第一运算级和在第一运算级之后的第二运算级,每个扩展数据运算逻辑模块包括:第一子模块,被配置为基于第一运算级的第2扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第0扩展寄存器中的扩展数据;第二子模块,被配置为基于第一运算级的第0扩展寄存器和第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;第三子模块,被配置为基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第二附加寄存器中的中间数据;以及第四子模块,被配置为基于第一运算级的第二附加寄存器中存储的中间数据和第一运算级的第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;其中,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据是第一运算级的第i扩展寄存器中存储的扩展数据,其中3≤i≤15且i为整数。

根据本公开的第四方面,提供了一种用于执行哈希算法的电路,包括:输入模块,被配置为接收数据;以及运算模块,被配置为基于接收到的数据计算哈希值,运算模块包括:以流水线结构布置的多个运算级,多个运算级中的每个运算级包括第0扩展寄存器至第15扩展寄存器以及第一附加寄存器,每个扩展寄存器被配置为存储当前运算级的扩展数据,第一附加寄存器被配置为存储用于计算扩展数据的中间数据;以及多个扩展数据运算逻辑模块,每个扩展数据运算逻辑模块设置在多个运算级中的相应的相邻两个运算级之间,相邻两个运算级包括第一运算级和在第一运算级之后的第二运算级,每个扩展数据运算逻辑模块包括:第一子模块,被配置为基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第一附加寄存器中的中间数据;第二子模块,被配置为基于第一运算级的第一附加寄存器中存储的中间数据和第一运算级的第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;第三子模块,被配置为基于第一运算级的第3扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第1扩展寄存器中的扩展数据;以及第四子模块,被配置为基于第一运算级的第1扩展寄存器和第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;其中,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据是第一运算级的第i扩展寄存器中存储的扩展数据,其中4≤i≤15且i为整数,并且用于存储到第二运算级的第0扩展寄存器中的扩展数据是第一运算级的第2扩展寄存器中存储的扩展数据。

位的数据,输出是256位的数据摘要,即哈希值。输入数据以512位的数据块为单位进行处理。为了实现sha-256算法,需要对于每个512位的数据块要进行64轮重复运算,因此可以采用包括64个运算级的流水线所示,该流水线运算级,每个运算级包括用于存储中间值的8个32位的压缩寄存器a至h以及用于存储扩展数据的16个32位的扩展寄存器r0至r15。第0运算级可以接收输入的数据块,并将其分成8个32位数据分别存入压缩寄存器a至h中,然后对其进行运算处理并提供给第1运算级。之后,每个运算级对其接收到的前一运算级的运算结果进行运算并将自己的运算结果提供给后一运算级。最终在经过64个运算级的运算后,运算核可以输出对输入数据执行过一次sha-256算法的哈希运算结果。下面详细讨论sha-256在每个运算级上进行的一轮运算的内部逻辑。在第t运算级上进行的第t轮运算由如下的运算式定义(t为整数且满足0≤t≤63):

具体地,图2示出了图1中的流水线结构中的相邻两个运算级的扩展寄存器中的扩展数据之间的常规运算逻辑。需要使用每个运算级的扩展寄存器r0、r1、r9和r14中的扩展数据来计算要存储在后一运算级的扩展寄存器r15中的扩展数据,另外扩展寄存器r1到r15中的扩展数据可以直接移位至后一运算级的相应扩展寄存器r0到r14中。具体而言,第t+1运算级的扩展寄存器r15中的扩展数据w15′是通过三个加法器add1、add2、add3将第t运算级的扩展寄存器r0中的扩展数据w0、经σ0运算器进行σ0运算后的第t运算级的扩展寄存器r1中的扩展数据σ0(w1)、第t运算级的扩展寄存器r9中的扩展数据w9、经σ1运算器进行σ1运算后的第t运算级的扩展寄存器r14中的扩展数据σ1(w14)依次相加得到的,即w15′=w0+σ0(w1)+w9+σ1(w14)。

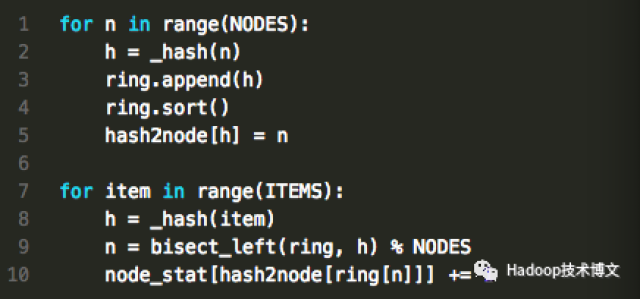

这样的场景的非限制性示例例如可以是用于执行sha-256算法的具有32个运算级的流水线示出了用于计算两个w参数的在第y运算级和第y+1运算级的扩展寄存器中的扩展数据之间的运算逻辑,其中0≤y≤31且y为整数。在图3中,用实线箭头指示用于计算第一w参数的数据移动方向,用点划线箭头指示用于计算第二w参数的数据移动方向,用点线指示直接移位而不经历运算的数据移动方向。如图3所示,第y+1运算级的扩展寄存器r14中的扩展数据w14′是通过三个加法器add11、add21、add31将第y运算级的扩展寄存器r0中的扩展数据w0、经σ01运算器进行σ0运算后的第y运算级的扩展寄存器r1中的扩展数据w1、第y运算级的扩展寄存器r9中的扩展数据w9、经σ11运算器进行σ1运算后的第y运算级的扩展寄存器r14中的扩展数据w14依次相加得到的,w14′=w0+σ0(w1)+w9+σ1(w14)。还如图3所示,第y+1运算级的扩展寄存器r15中的扩展数据w15′是通过三个加法器add12、add22、add32将第y运算级的扩展寄存器r1中的扩展数据w1、经σ02运算器进行σ0运算后的第y运算级的扩展寄存器r2中的扩展数据w2、第y运算级的扩展寄存器r10中的扩展数据w10、经σ12运算器进行σ1运算后的第y运算级的扩展寄存器r15中的扩展数据w15依次相加得到的,w15′=w1+σ0(w2)+w10+σ1(w15)。由此,这样一轮运算后可以计算出两个w参数(w14′和w15′)。另外,第y运算级的第2扩展寄存器至第15扩展寄存器中的每个扩展寄存器中存储的扩展数据直接移位到第y+1运算级的第0扩展寄存器至第13扩展寄存器中的相应扩展寄存器中。

然而,从第y运算级的扩展寄存器r0、r1、r9和r14中的扩展数据计算要存储在第y+1运算级的扩展寄存器r14中的扩展数据需要经历的运算逻辑级数包括4级。从第y运算级的扩展寄存器r1、r2、r10和r15中的扩展数据计算要存储在第y+1运算级的扩展寄存器r15中的扩展数据需要经历的运算逻辑级数包括4级。因而,即使并行处理这两个w参数的计算过程,需要经历的运算逻辑级数也高达4级,这带来了显著的计算延时,限制了流水线结构的运算速度,难以进一步实现更低的功耗算力比。

对此,本申请的发明人注意到,第y+1运算级的扩展寄存器r0与第y运算级的扩展寄存器r2二者之间存在直连关系,即第y运算级的扩展寄存器r2中存储的扩展数据被直接移位至第y+1运算级的扩展寄存器r0。因此,本申请的发明人想到,可以利用扩展寄存器r0与r2的这一直连关系,将用于计算第y+2运算级的扩展寄存器r14中要存储的扩展数据的过程中涉及第y+1运算级的扩展寄存器r0中的扩展数据(即第y运算级的扩展寄存器r2中的扩展数据)的部分提前到与用于计算第y+1运算级的扩展寄存器r14中要存储的扩展数据的过程同时进行,并存入第y+1运算级的扩展寄存器r0。这样,可以在将用于计算第y+2运算级的扩展寄存器r14中要存储的扩展数据的过程进行拆解后,将拆解出的部分与用于计算第y+1运算级的扩展寄存器r14中要存储的扩展数据的过程并行地处理。通过并行处理,可以减少每轮运算中计算扩展数据所需要经历的运算逻辑级数。

同样,本申请的发明人也注意到,第y+1运算级的扩展寄存器r1与第y运算级的扩展寄存器r3二者之间存在直连关系,即第y运算级的扩展寄存器r3中存储的扩展数据被直接移位至第y+1运算级的扩展寄存器r1。因此,本申请的发明人想到,可以利用扩展寄存器r1与r3的这一直连关系,将用于计算第y+2运算级的扩展寄存器r15中要存储的扩展数据的过程中涉及第y+1运算级的扩展寄存器r1中的扩展数据(即第y运算级的扩展寄存器r3中的扩展数据)的部分提前到与用于计算第y+1运算级的扩展寄存器r15中要存储的扩展数据的过程同时进行,并存入第y+1运算级的扩展寄存器r1。这样,可以在将用于计算第y+2运算级的扩展寄存器r15中要存储的扩展数据的过程进行拆解后,将拆解出的部分与用于计算第y+1运算级的扩展寄存器r15中要存储的扩展数据的过程并行地处理。通过并行处理,可以减少每轮运算中计算扩展数据所需要经历的运算逻辑级数。

通常,运算模块120的最前一个运算级120-0的第0扩展寄存器r0至第15扩展寄存器r15中存储的扩展数据例如可以直接取自由输入模块110接收的数据,而从运算级120-1开始的每个运算级的第0扩展寄存器r0至第15扩展寄存器r15中要存储的扩展数据例如可以基于前一运算级的第0扩展寄存器r0至第15扩展寄存器r15中存储的扩展数据确定。本公开主要讨论的是如何基于前一运算级的第0扩展寄存器r0至第15扩展寄存器r15中存储的扩展数据确定后一运算级的第0扩展寄存器r0至第15扩展寄存器r15中要存储的扩展数据。

运算模块120还可以包括多个扩展数据运算逻辑模块130,每个扩展数据运算逻辑模块130设置在运算模块120的多个运算级120-0、…、120-31中的相应的相邻两个运算级之间。在本文中,可以将相邻两个运算级中在前的运算级称为第一运算级并将相邻两个运算级中在后的运算级称为第二运算级,注意″第一″和″第二″仅是用于区分而非限制性的。例如,如图4所示,相邻两个运算级120-a、120-b之间设置有扩展数据运算逻辑模块130。每个扩展数据运算逻辑模块130可以包括第一子模块131、第二子模块132、第三子模块133和第四子模块134。

扩展数据运算逻辑模块130可以被配置用于基于第一运算级(例如,120-a)的扩展寄存器中存储的扩展数据计算用于存储到第二运算级(例如,120-b)的扩展寄存器中的扩展数据。第一子模块131可以被配置为基于第一运算级的第2扩展寄存器r2中存储的扩展数据计算用于存储到第二运算级的第0扩展寄存器r0中的扩展数据。第二子模块132可以被配置为基于第一运算级的第0扩展寄存器r0和第14扩展寄存器r14中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器r14中的扩展数据。第三子模块133可以被配置为基于第一运算级的第3扩展寄存器r3中存储的扩展数据计算用于存储到第二运算级的第1扩展寄存器r1中的扩展数据。第四子模块134可以被配置为基于第一运算级的第1扩展寄存器r1和第15扩展寄存器r15中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器r15中的扩展数据。另外,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据可以是第一运算级的第i扩展寄存器中存储的扩展数据,其中4≤i≤15且i为整数。第一子模块131和第二子模块132可以用于计算第一w参数。第三子模块133和第四子模块134可以用于计算第二w参数。

下面结合图5至图7描述根据本公开的实施例的如图4所示的电路100中包括扩展数据运算逻辑模块的部分的几种非限制性示例配置,其示出了第一子模块131和第二子模块132的协作方式与第三子模块133和第四子模块134的协作方式的几种非限制性示例组合。在这些图中,以相邻两个运算级120-a和120-b为例进行说明,可以理解,在运算模块120中的任意相邻两个运算级都可以是以下讨论的运算级120-a和120-b。另外,在这些图中,为了清楚起见,用点线箭头指示直接移位而不经过运算的扩展数据的移动方向,用实线箭头指示经由第一子模块131和第二子模块132处理的扩展数据的移动方向,用点划线箭头指示经由第三子模块133和第四子模块134处理的扩展数据的移动方向,第一子模块至第四子模块131-134的示意性框图在下方另行给出。

在如图5所示的示例中,运算级120-b的第0扩展寄存器r0中的扩展数据w0′是通过由第一子模块131处理运算级120-a的第2扩展寄存器r2中存储的扩展数据w2、第3扩展寄存器r3中存储的扩展数据w3和第11扩展寄存器r11中存储的扩展数据w11得到的。具体地,在这个示例中,第一子模块131包括用于执行σ0运算的σ01运算器和用于执行加法运算的全加器faa1和加法器add1,其中扩展数据w3被输入到σ01运算器,σ01运算器的输出、扩展数据w2和扩展数据w11被输入到全加器faa1,全加器faa1的输出被输入到加法器add1,加法器add1的输出被提供给运算级120-b的第0扩展寄存器r0,使得w0′=w2+σ0(w3)+w11。

进一步如图5所示,运算级120-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块132处理运算级120-a的第0扩展寄存器r0中存储的扩展数据w0和第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块132包括用于执行σ1运算的σ11运算器以及用于执行加法运算的加法器add2,其中扩展数据w14被输入到σ11运算器,σ11运算器的输出和扩展数据w0被输入到加法器add2,加法器add2的输出被提供给运算级120-b的第14扩展寄存器r14,使得w14′=w0+σ1(w14)。

进一步如图5所示,运算级120-b的第1扩展寄存器r1中的扩展数据w1′是通过由第三子模块133处理运算级120-a的第3扩展寄存器r3中存储的扩展数据w3、第4扩展寄存器r4中存储的扩展数据w4和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块133包括用于执行σ0运算的σ02运算器以及用于执行加法运算的全加器faa2和加法器add3,其中扩展数据w4被输入到σ02运算器,σ02运算器的输出、扩展数据w3和扩展数据w12被输入到全加器faa2,全加器faa2的输出被输入到加法器add3,加法器add3的输出被提供给运算级120-b的第1扩展寄存器r1,使得w1′=w3+σ0(w4)+w12。

进一步如图5所示,运算级120-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块134处理运算级120-a的第1扩展寄存器r1中存储的扩展数据w1和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块134包括用于执行σ1运算的σ12运算器以及用于执行加法运算的加法器add4,其中扩展数据w15被输入到σ12运算器,σ12运算器的输出和扩展数据w1被输入到加法器add4,加法器add4的输出被提供给运算级120-b的第15扩展寄存器r15,使得w15′=w1+σ1(w15)。

在如图6所示的示例中,运算级120-b的第0扩展寄存器r0中的扩展数据w0′是通过由第一子模块131处理运算级120-a的第2扩展寄存器r2中存储的扩展数据w2和第3扩展寄存器r3中存储的扩展数据w3得到的。具体地,在这个示例中,第一子模块131包括σ01运算器和加法器add1,其中扩展数据w3被输入到σ01运算器,σ01运算器的输出和扩展数据w2被输入到加法器add1,加法器add1的输出被提供给运算级120-b的第0扩展寄存器r0,使得w0′=w2+σ0(w3)。

进一步如图6所示,运算级120-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块132处理运算级120-a的第0扩展寄存器r0中存储的扩展数据w0、第9扩展寄存器r9中存储的扩展数据w9和第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块132包括σ11运算器、全加器faa1和加法器add2,其中扩展数据w14被输入到σ11运算器,σ11运算器的输出、扩展数据w0和扩展数据w9被输入到全加器faa1,全加器faa1的输出被输入到加法器add2,加法器add2的输出被提供给运算级120-b的第14扩展寄存器r14,使得w14′=w0+w9+σ1(w14)。

进一步如图6所示,运算级120-b的第1扩展寄存器r1中的扩展数据w1′是通过由第三子模块133处理运算级120-a的第3扩展寄存器r3中存储的扩展数据w3和第4扩展寄存器r4中存储的扩展数据w4得到的。具体地,在这个示例中,第三子模块133包括σ02运算器和加法器add3,其中扩展数据w4被输入到σ02运算器,σ02运算器的输出和扩展数据w3被输入到加法器add3,加法器add3的输出被提供给运算级120-b的第1扩展寄存器r1,使得w1′=w3+σ0(w4)。

进一步如图6所示,运算级120-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块134处理运算级120-a的第1扩展寄存器r1中存储的扩展数据w1、第10扩展寄存器r10中存储的扩展数据w10和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块134包括σ12运算器、全加器faa2和加法器add4,其中扩展数据w15被输入到σ12运算器,σ12运算器的输出、扩展数据w1和扩展数据w10被输入到全加器faa2,全加器faa2的输出被输入到加法器add4,加法器add4的输出被提供给运算级120-b的第15扩展寄存器r15,使得w15′=w1+w10+σ1(w15)。

进一步如图7所示,运算级120-b的第1扩展寄存器r1中的扩展数据w1′是通过由第三子模块133处理运算级120-a的第3扩展寄存器r3中存储的扩展数据w3和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块133包括加法器add3,其中扩展数据w3和w12被输入到加法器add3,加法器add3的输出被提供给运算级120-b的第1扩展寄存器r1,使得w1′=w3+w12。

进一步如图7所示,运算级120-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块134处理运算级120-a的第1扩展寄存器r1中存储的扩展数据w1、第2扩展寄存器r2中存储的扩展数据w2和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块134包括σ02运算器、σ12运算器、全加器faa2和加法器add4,其中扩展数据w2被输入到σ02运算器,扩展数据w15被输入到σ12运算器,σ0运算与σ1运算可以同时进行。然后σ02运算器的输出、σ12运算器的输出和扩展数据w1被输入到全加器faa2,全加器faa2的输出被输入到加法器add4,加法器add4的输出被提供给运算级120-b的第15扩展寄存器r15,使得w15′=w1+σ0(w2)+σ1(w15)。

相应地,本公开也提供了在用于执行哈希算法的电路中计算扩展数据的方法。图18示出了根据本公开的实施例的在用于执行哈希算法的电路中计算扩展数据的方法500的示例性流程图。这样的电路可以包括被配置为接收数据的输入模块和被配置为基于接收到的数据计算哈希值的运算模块,其中运算模块可以包括以流水线结构布置的多个运算级,每个运算级包括第0扩展寄存器至第15扩展寄存器,每个扩展寄存器可以被配置为存储当前运算级的扩展数据。对于运算模块的多个运算级中的包括第一运算级和在第一运算级之后的第二运算级的相邻两个运算级,方法500可以包括:在s501处,基于第一运算级的第2扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第0扩展寄存器中的扩展数据;在s502处,基于第一运算级的第0扩展寄存器和第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;在s503处,基于第一运算级的第3扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第1扩展寄存器中的扩展数据;在s504处,基于第一运算级的第1扩展寄存器和第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;在s505处,将第一运算级的第i扩展寄存器中存储的扩展数据作为用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据,其中4≤i≤15且i为整数。注意,s501-s505并不需要以顺序次序执行,而是可以以任何次序执行,或者可以至少部分地并行执行。

此外,在根据本公开的上述实施例的电路和方法中,使用扩展寄存器r0、r1来存储提前进行的在原本用于计算后续运算级的扩展寄存器r14、r15中要存储的扩展数据的过程中涉及先前运算级的扩展寄存器r2、r3中的扩展数据的部分。在一些替代实施例中,也可以使用附加的寄存器来替代地实现扩展寄存器r0、r1在上述实施例中所起到的作用。而且,当使用附加的寄存器时,不仅可以用于提前进行在原本用于计算后续运算级的扩展寄存器r14、r15中要存储的扩展数据的过程中涉及先前运算级的扩展寄存器r0、r1中的扩展数据的部分,而且可以提前进行在原本用于计算后续运算级的扩展寄存器r14、r15中要存储的扩展数据的过程的任何合适部分。

图8示出了根据本公开的另外一些实施例的用于执行哈希算法的电路200的示意性框图。其中箭头表示数据传递方向。电路200可以包括输入模块210和运算模块220。输入模块210可以被配置为接收数据。运算模块220可以被配置为基于接收到的数据计算哈希值。运算模块220可以包括以流水线,每个运算级可以包括第0扩展寄存器r0至第15扩展寄存器r15以及第一附加寄存器x1和第二附加寄存器x2。每个扩展寄存器可以被配置为存储当前运算级的扩展数据,每个附加寄存器可以被配置为存储用于计算扩展数据的中间数据。在一些实施例中,在最前一个运算级220-0中,第一附加寄存器x1中的中间数据可以与第0扩展寄存器r0中的扩展数据相同,第二附加寄存器x2中的中间数据可以与第1扩展寄存器r1中的扩展数据相同。

运算模块220还可以包括多个扩展数据运算逻辑模块230,每个扩展数据运算逻辑模块230设置在运算模块220的多个运算级220-0、…、220-31中的相应的相邻两个运算级之间。在本文中,可以将相邻两个运算级中在前的运算级称为第一运算级并将相邻两个运算级中在后的运算级称为第二运算级,注意″第一″和″第二″仅是用于区分而非限制性的。例如,如图8所示,相邻两个运算级220-a、220-b之间设置有扩展数据运算逻辑模块230。每个扩展数据运算逻辑模块230可以包括第一子模块231、第二子模块232、第三子模块233和第四子模块234。

第一子模块231可以被配置为基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第一附加寄存器x1中的中间数据。第二子模块232可以被配置为基于第一运算级的第一附加寄存器x1中存储的中间数据和第14扩展寄存器r14中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器r14中的扩展数据。第三子模块233可以被配置为基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第二附加寄存器x2中的中间数据。第四子模块234可以被配置为基于第一运算级的第二附加寄存器x2中存储的中间数据和第15扩展寄存器r15中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器r15中的扩展数据。另外,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据可以是第一运算级的第i扩展寄存器中存储的扩展数据,其中2≤i≤15且i为整数。第一子模块231和第二子模块232可以用于计算第一w参数。第三子模块233和第四子模块234可以用于计算第二w参数。

下面结合图9至图12描述根据本公开的实施例的如图8所示的电路200中包括扩展数据运算逻辑模块的部分的几种非限制性示例配置,其示出了第一子模块231和第二子模块232的协作方式与第三子模块233和第四子模块234的协作方式的几种非限制性示例组合。在这些图中,以相邻两个运算级220-a和220-b为例进行说明,可以理解,在运算模块220中的任意相邻两个运算级都可以是以下讨论的运算级220-a和220-b。另外,在这些图中,为了清楚起见,用点线箭头指示直接移位而不经过运算的扩展数据的移动方向,用实线箭头指示经由第一子模块231和第二子模块232处理的扩展数据的移动方向,用点划线箭头指示经由第三子模块233和第四子模块234处理的扩展数据的移动方向,第一子模块至第四子模块231-234的示意性框图在下方另行给出。

在如图9所示的示例中,运算级220-b的第一附加寄存器x1中的中间数据wx1′是通过由第一子模块231处理运算级220-a的第2扩展寄存器r2中存储的扩展数据w2、第3扩展寄存器r3中存储的扩展数据w3和第11扩展寄存器r11中存储的扩展数据w11得到的。具体地,在这个示例中,第一子模块231包括σ01运算器、全加器faa1和加法器add1,其中扩展数据w3被输入到σ01运算器,σ01运算器的输出、扩展数据w2和扩展数据w11被输入到全加器faa1,全加器faa1的输出被输入到加法器add1,加法器add1的输出被提供给运算级220-b的第一附加寄存器x1,使得wx1′=w2+σ0(w3)+w11。

进一步如图9所示,运算级220-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块232处理运算级220-a的第一附加寄存器x1中存储的中间数据wx1和运算级220-a的第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块232包括σ11运算器和加法器add2,其中扩展数据w14被输入到σ11运算器,σ11运算器的输出和中间数据wx1被输入到加法器add2,加法器add2的输出被提供给运算级220-b的第14扩展寄存器r14,使得w14′=wx1+σ1(w14)。

进一步如图9所示,运算级220-b的第二附加寄存器x2中的中间数据wx2′是通过由第三子模块233处理运算级220-a的第3扩展寄存器r3中存储的扩展数据w3、第4扩展寄存器r4中存储的扩展数据w4和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块233包括σ02运算器、全加器faa2和加法器add3,其中扩展数据w4被输入到σ02运算器,σ02运算器的输出、扩展数据w3和扩展数据w12被输入到全加器faa2,全加器faa2的输出被输入到加法器add3,加法器add3的输出被提供给运算级220-b的第二附加寄存器x2,使得wx2′=w3+σ0(w4)+w12。

进一步如图9所示,运算级220-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块234处理运算级220-a的第二附加寄存器x2中存储的中间数据wx2和运算级220-a的第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块234包括σ12运算器和加法器add4,其中扩展数据w15被输入到σ12运算器,σ12运算器的输出和中间数据wx2被输入到加法器add4,加法器add4的输出被提供给运算级220-b的第15扩展寄存器r15,使得w15′=wx2+σ1(w15)。

在如图10所示的示例中,运算级220-b的第一附加寄存器x1中的中间数据wx1′是通过由第一子模块231处理运算级220-a的第2扩展寄存器r2中存储的扩展数据w2和第3扩展寄存器r3中存储的扩展数据w3得到的。具体地,在这个示例中,第一子模块231包括σ01运算器和加法器add1,其中扩展数据w3被输入到σ01运算器,σ01运算器的输出和扩展数据w2被输入到加法器add1,加法器add1的输出被提供给运算级220-b的第一附加寄存器x1,使得wx1′=w2+σ0(w3)。

进一步如图10所示,运算级220-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块232处理运算级220-a的第一附加寄存器x1中存储的中间数据wx1、第9扩展寄存器r9中存储的扩展数据w9和第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块232包括σ11运算器、全加器faa1和加法器add2,其中扩展数据w14被输入到σ11运算器,σ11运算器的输出、中间数据wx1和扩展数据w9被输入到全加器faa1,全加器faa1的输出被输入到加法器add2,加法器add2的输出被提供给运算级220-b的第14扩展寄存器r14,使得w14′=wx1+w9+σ1(w14)。

进一步如图10所示,运算级220-b的第二附加寄存器x2中的中间数据wx2′是通过由第三子模块233处理运算级220-a的第3扩展寄存器r3中存储的扩展数据w3和第4扩展寄存器r4中存储的扩展数据w4得到的。具体地,在这个示例中,第三子模块233包括σ02运算器和加法器add3,其中扩展数据w4被输入到σ02运算器,σ02运算器的输出和扩展数据w3被输入到加法器add3,加法器add3的输出被提供给运算级220-b的第二附加寄存器x2,使得wx2′=w3+σ0(w4)。

进一步如图10所示,运算级220-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块234处理运算级220-a的第二附加寄存器x2中存储的中间数据wx2、第10扩展寄存器r10中存储的扩展数据w10和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块234包括σ12运算器、全加器faa2和加法器add4,其中扩展数据w15被输入到σ12运算器,σ12运算器的输出、中间数据wx2和扩展数据w10被输入到全加器faa2,全加器faa2的输出被输入到加法器add4,加法器add4的输出被提供给运算级220-b的第15扩展寄存器r15,使得w15′=wx2+w10+σ1(w15)。

在如图11所示的示例中,运算级220-b的第一附加寄存器x1中的中间数据wx1′是通过由第一子模块231处理运算级220-a的第2扩展寄存器r2中存储的扩展数据w2和第11扩展寄存器r11中存储的扩展数据w11得到的。具体地,在这个示例中,第一子模块231包括加法器add1,其中扩展数据w2和w11被输入到加法器add1,加法器add1的输出被提供给运算级220-b的第一附加寄存器x1,使得wx1′=w2+w11。

进一步如图11所示,运算级220-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块232处理运算级220-a的第一附加寄存器x1中存储的中间数据wx1、第1扩展寄存器r1中存储的扩展数据w1和第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块232包括σ01运算器、σ11运算器、全加器faa1和加法器add2。扩展数据w1被输入到σ01运算器,扩展数据w14被输入到σ11运算器,σ0运算和σ1运算可以同时进行。然后,σ01运算器的输出、σ11运算器的输出和中间数据wx1被输入到全加器faa1,全加器faa1的输出被输入到加法器add2,加法器add2的输出被提供给运算级220-b的第14扩展寄存器r14,使得w14′=wx1+σ0(w1)+σ1(w14)。

进一步如图11所示,运算级220-b的第二附加寄存器x2中的中间数据wx2′是通过由第三子模块233处理运算级220-a的第3扩展寄存器r3中存储的扩展数据w3和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块233包括加法器add3,其中扩展数据w3和w12被输入到加法器add3,加法器add3的输出被提供给运算级220-b的第二附加寄存器x2,使得wx2′=w3+w12。

进一步如图11所示,运算级220-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块234处理运算级220-a的第二附加寄存器x2中存储的中间数据wx2、第2扩展寄存器r2中存储的扩展数据w2和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块234包括σ02运算器、σ12运算器、全加器faa2和加法器add4,其中扩展数据w2被输入到σ02运算器,扩展数据w15被输入到σ12运算器,σ0运算与σ1运算可以同时进行。然后σ02运算器的输出、σ12运算器的输出和中间数据wx2被输入到全加器faa2,全加器faa2的输出被输入到加法器add4,加法器add4的输出被提供给运算级220-b的第15扩展寄存器r15,使得w15′=wx2+σ0(w2)+σ1(w15)。

在如图12所示的示例中,运算级220-b的第一附加寄存器x1中的中间数据wx1′是通过由第一子模块231处理运算级220-a的第3扩展寄存器r3中存储的扩展数据w3和第11扩展寄存器r11中存储的扩展数据w11得到的。具体地,在这个示例中,第一子模块231包括σ01运算器和加法器add1,其中扩展数据w3被输入到σ01运算器,σ01运算器的输出和扩展数据w11被输入到加法器add1,加法器add1的输出被提供给运算级220-b的第一附加寄存器x1,使得wx1′=σ0(w3)+w11。

进一步如图12所示,运算级220-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块232处理运算级220-a的第一附加寄存器x1中存储的中间数据wx1、第0扩展寄存器r0中存储的扩展数据w0和第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块232包括σ11运算器、全加器faa1和加法器add2,其中扩展数据w14被输入到σ11运算器,σ11运算器的输出、扩展数据w0和中间数据wx1被输入到全加器faa1,全加器faa1的输出被输入到加法器add2,加法器add2的输出被提供给运算级220-b的第14扩展寄存器r14,使得w14′=wx1+w0+σ1(w14)。

进一步如图12所示,运算级220-b的第二附加寄存器x2中的中间数据wx2′是通过由第三子模块233处理运算级220-a的第4扩展寄存器r4中存储的扩展数据w4和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块233包括σ02运算器和加法器add3,其中扩展数据w4被输入到σ02运算器,σ02运算器的输出和扩展数据w12被输入到加法器add3,加法器add3的输出被提供给运算级220-b的第二附加寄存器x2,使得wx2′=σ0(w4)+w12。

进一步如图12所示,运算级220-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块234处理运算级220-a的第二附加寄存器x2中存储的中间数据wx2、第1扩展寄存器r1中存储的扩展数据w1和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块234包括σ12运算器、全加器faa2和加法器add4,其中扩展数据w15被输入到σ12运算器,σ12运算器的输出、扩展数据w1和中间数据wx2被输入到全加器faa2,全加器faa2的输出被输入到加法器add4,加法器add4的输出被提供给运算级220-b的第15扩展寄存器r15,使得w15′=wx2+w1+σ1(w15)。

相应地,本公开也提供了在用于执行哈希算法的电路中计算扩展数据的方法。图19示出了根据本公开的实施例的在用于执行哈希算法的电路中计算扩展数据的方法600的示例性流程图。这样的电路可以包括被配置为接收数据的输入模块和被配置为基于接收到的数据计算哈希值的运算模块,其中运算模块可以包括以流水线结构布置的多个运算级,每个运算级包括第0扩展寄存器至第15扩展寄存器以及第一附加寄存器和第二附加寄存器,每个扩展寄存器被配置为存储当前运算级的扩展数据,每个附加寄存器被配置为存储用于计算扩展数据的中间数据。对于运算模块的多个运算级中的包括第一运算级和在第一运算级之后的第二运算级的相邻两个运算级,方法600可以包括:在s601处,基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第一附加寄存器中的中间数据;在s602处,基于第一运算级的第一附加寄存器中存储的中间数据和第一运算级的第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;在s603处,基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第二附加寄存器中的中间数据;在s604处,基于第一运算级的第二附加寄存器中存储的中间数据和第一运算级的第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;在s605处,将第一运算级的第i扩展寄存器中存储的扩展数据作为用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据,其中2≤i≤15且i为整数。注意,s601-s605并不需要以顺序次序执行,而是可以以任何次序执行,或者可以至少部分地并行执行。

例如,图13示出了根据本公开的另外一些实施例的用于执行哈希算法的电路300的示意性框图。其中箭头表示数据传递方向。电路300可以包括输入模块310和运算模块320。输入模块310可以被配置为接收数据。运算模块320可以被配置为基于接收到的数据计算哈希值。运算模块320还可以包括多个扩展数据运算逻辑模块330,每个扩展数据运算逻辑模块330设置在运算模块320的多个运算级320-0、…、320-31中的相应的相邻两个运算级(例如,320-a与320-b)之间。

电路300与电路100、200相比,区别在于电路300的运算模块320的每个运算级可以包括第0扩展寄存器r0至第15扩展寄存器r15和第二附加寄存器x2而没有包括第一附加寄存器x1,并且相应地,每个扩展数据运算逻辑模块330可以包括如前所述的第一子模块131、第二子模块132、第三子模块233和第四子模块234。在一些实施例中,在最前一个运算级320-0中,第二附加寄存器x2中的中间数据可以与第1扩展寄存器r1中的扩展数据相同。

在电路300中:第一子模块131可以被配置为基于第一运算级(例如,320-a)的第2扩展寄存器r2中存储的扩展数据计算用于存储到第二运算级(例如,320-b)的第0扩展寄存器r0中的扩展数据;第二子模块132可以被配置为基于第一运算级的第0扩展寄存器r0和第14扩展寄存器r14中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器r14中的扩展数据;第三子模块233可以被配置为基于第一运算级的扩展寄存器r3中存储的扩展数据计算用于存储到第二运算级的第二附加寄存器x2中的中间数据;以及第四子模块234可以被配置为基于第一运算级的第二附加寄存器x2中存储的中间数据和第15扩展寄存器r15中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器r15中的扩展数据。另外,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据可以是第一运算级的第i扩展寄存器中存储的扩展数据,其中3≤i≤15且i为整数。在电路300中,第一子模块131和第二子模块132可以用于计算第一w参数,第三子模块233和第四子模块234可以用于计算第二w参数。

如前所述,第一子模块131和第二子模块132可以采用多种协作方式来计算扩展数据,从而提供第一w参数,其实施例在此不再赘述。同样,如前所述,第三子模块233和第四子模块234可以采用多种协作方式来计算扩展数据,从而提供第二w参数,其实施例在此亦不再赘述。在电路300的各种实现方式中,根据本公开的实施例的第一子模块131和第二子模块132的任一协作方式与第三子模块233和第四子模块234的任一协作方式可以自由组合,从而提供第一w参数和第二w参数。

下面结合图14和图15描述根据本公开的实施例的如图13所示的电路300中包括扩展数据运算逻辑模块的部分的几种非限制性示例配置,其示出了第一子模块131和第二子模块132的协作方式与第三子模块233和第四子模块234的协作方式的几种非限制性示例组合。在这些图中,以相邻两个运算级320-a和320-b为例进行说明,可以理解,在运算模块320中的任意相邻两个运算级都可以是以下讨论的运算级320-a和320-b。另外,在这些图中,为了清楚起见,用点线箭头指示直接移位而不经过运算的扩展数据的移动方向,用实线箭头指示经由第一子模块131和第二子模块132处理的扩展数据的移动方向,用点划线箭头指示经由第三子模块233和第四子模块234处理的扩展数据的移动方向,第一子模块至第四子模块的示意性框图在下方另行给出。

在如图14所示的示例中,运算级320-b的第0扩展寄存器r0中的扩展数据w0′是通过由第一子模块131处理运算级320-a的第2扩展寄存器r2中存储的扩展数据w2、第3扩展寄存器r3中存储的扩展数据w3和第11扩展寄存器r11中存储的扩展数据w11得到的。具体地,在这个示例中,第一子模块131包括σ01运算器、全加器faa1和加法器add1,其中扩展数据w3被输入到σ01运算器,σ01运算器的输出、扩展数据w2和扩展数据w11被输入到全加器faa1,全加器faa1的输出被输入到加法器add1,加法器add1的输出被提供给运算级320-b的第0扩展寄存器r0,使得w0′=w2+σ0(w3)+w11。

进一步如图14所示,运算级320-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块132处理运算级320-a的第0扩展寄存器r0中存储的扩展数据w0和第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块132包括σ11运算器和加法器add2,其中扩展数据w14被输入到σ11运算器,σ11运算器的输出和扩展数据w0被输入到加法器add2,加法器add2的输出被提供给运算级320-b的第14扩展寄存器r14,使得w14′=w0+σ1(w14)。

进一步如图14所示,运算级320-b的第二附加寄存器x2中的中间数据wx2′是通过由第三子模块233处理运算级320-a的第3扩展寄存器r3中存储的扩展数据w3、第4扩展寄存器r4中存储的扩展数据w4和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块233包括σ02运算器、全加器faa2和加法器add3,其中扩展数据w4被输入到σ02运算器,σ02运算器的输出、扩展数据w3和扩展数据w12被输入到全加器faa2,全加器faa2的输出被输入到加法器add3,加法器add3的输出被提供给运算级320-b的第二附加寄存器x2,使得wx2′=w3+σ0(w4)+w12。

进一步如图14所示,运算级320-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块234处理运算级320-a的第二附加寄存器x2中存储的中间数据wx2和运算级220-a的第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块234包括σ12运算器和加法器add4,其中扩展数据w15被输入到σ12运算器,σ12运算器的输出和中间数据wx2被输入到加法器add4,加法器add4的输出被提供给运算级320-b的第15扩展寄存器r15,使得w15′=wx2+σ1(w15)。

在如图15所示的示例中,运算级320-b的第0扩展寄存器r0中的扩展数据w0′是通过由第一子模块131处理运算级320-a的第2扩展寄存器r2中存储的扩展数据w2和第11扩展寄存器r11中存储的扩展数据w11得到的。具体地,在这个示例中,第一子模块131包括加法器add1,其中扩展数据w2和w11被输入到加法器add1,加法器add1的输出被提供给运算级320-b的第0扩展寄存器r0,使得w0′=w2+w11。

进一步如图15所示,运算级320-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块132处理运算级320-a的第0扩展寄存器r0中存储的扩展数据w0、第1扩展寄存器r1中存储的扩展数据w1和第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块132包括σ01运算器、σ11运算器、全加器faa1和加法器add2,其中w1被输入到σ01运算器,扩展数据w14被输入到σ11运算器,σ0运算和σ1运算可以同时进行。然后,σ01运算器的输出、σ11运算器的输出和扩展数据w0被输入到全加器faa1,全加器faa1的输出被输入到加法器add2,加法器add2的输出被提供给运算级320-b的第14扩展寄存器r14,使得w14′=w0+σ0(w1)+σ1(w14)。

进一步如图15所示,运算级320-b的第二附加寄存器x2中的中间数据wx2′是通过由第三子模块233处理运算级320-a的第3扩展寄存器r3中存储的扩展数据w3和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块233包括加法器add3,其中扩展数据w3和w12被输入到加法器add3,加法器add3的输出被提供给运算级320-b的第二附加寄存器x2,使得wx2′=w3+w12。

进一步如图15所示,运算级320-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块234处理运算级220-a的第二附加寄存器x2中存储的中间数据wx2、第2扩展寄存器r2中存储的扩展数据w2和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块234包括σ02运算器、σ12运算器、全加器faa2和加法器add4,其中扩展数据w2被输入到σ02运算器,扩展数据w15被输入到σ12运算器,σ0运算与σ1运算可以同时进行。然后σ02运算器的输出、σ12运算器的输出和中间数据wx2被输入到全加器faa2,全加器faa2的输出被输入到加法器add4,加法器add4的输出被提供给运算级320-b的第15扩展寄存器r15,使得w15′=wx2+σ0(w2)+σ1(w15)。

相应地,本公开也提供了在用于执行哈希算法的电路中计算扩展数据的方法。图20示出了根据本公开的实施例的在用于执行哈希算法的电路中计算扩展数据的方法700的示例性流程图。这样的电路可以包括被配置为接收数据的输入模块和被配置为基于接收到的数据计算哈希值的运算模块,其中运算模块可以包括以流水线结构布置的多个运算级,每个运算级包括第0扩展寄存器至第15扩展寄存器以及第二附加寄存器,每个扩展寄存器被配置为存储当前运算级的扩展数据,第二附加寄存器被配置为存储用于计算扩展数据的中间数据。对于运算模块的多个运算级中的包括第一运算级和在第一运算级之后的第二运算级的相邻两个运算级,方法700可以包括:在s701处,基于第一运算级的第2扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第0扩展寄存器中的扩展数据;在s702处,基于第一运算级的第0扩展寄存器和第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;在s703处,基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第二附加寄存器中的中间数据;在s704处,基于第一运算级的第二附加寄存器中存储的中间数据和第一运算级的第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;在s705处,将第一运算级的第i扩展寄存器中存储的扩展数据作为用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据,其中3≤i≤15且i为整数。注意,s701-s705并不需要以顺序次序执行,而是可以以任何次序执行,或者可以至少部分地并行执行。

又例如,例如,图16示出了根据本公开的另外一些实施例的用于执行哈希算法的电路400的示意性框图。其中箭头表示数据传递方向。电路400可以包括输入模块410和运算模块420。输入模块410可以被配置为接收数据。运算模块420可以被配置为基于接收到的数据计算哈希值。运算模块420还可以包括多个扩展数据运算逻辑模块430,每个扩展数据运算逻辑模块430设置在运算模块420的多个运算级420-0、…、420-31中的相应的相邻两个运算级(例如,420-a与420-b)之间。

电路400与电路100、200相比,区别在于电路400的运算模块420的每个运算级可以包括第0扩展寄存器r0至第15扩展寄存器r15和第一附加寄存器x1而没有包括第二附加寄存器x2,并且相应地,每个扩展数据运算逻辑模块430可以包括如前所述的第一子模块231、第二子模块232、第三子模块133和第四子模块134。在一些实施例中,在最前一个运算级220-0中,第一附加寄存器x1中的中间数据可以与第0扩展寄存器r0中的扩展数据相同。

在电路400中:第一子模块231可以被配置为基于第一运算级(例如,420-a)的扩展寄存器r2中存储的扩展数据计算用于存储到第二运算级(例如,420-b)的第一附加寄存器x1中的中间数据;第二子模块232可以被配置为基于第一运算级的第一附加寄存器x1中存储的中间数据和第一运算级的第14扩展寄存器r14中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器r14中的扩展数据;第三子模块133可以被配置为基于第一运算级的第3扩展寄存器r3中存储的扩展数据计算用于存储到第二运算级的第1扩展寄存器r1中的扩展数据;第四子模块134可以被配置为基于第一运算级的第1扩展寄存器r1和第15扩展寄存器r15中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器r15中的扩展数据。另外,用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据可以是第一运算级的第i扩展寄存器中存储的扩展数据,其中4≤i≤15且i为整数,并且用于存储到第二运算级的第0扩展寄存器中的扩展数据是第一运算级的第2扩展寄存器中存储的扩展数据。在电路400中,第一子模块231和第二子模块232可以用于计算第一w参数,第三子模块133和第四子模块134可以用于计算第二w参数。

如前所述,第一子模块231和第二子模块232可以采用多种协作方式来计算扩展数据,从而提供第一w参数,其实施例在此不再赘述。同样,如前所述,第三子模块133和第四子模块134可以采用多种协作方式来计算扩展数据,从而提供第二w参数,其实施例在此亦不再赘述。在电路400的各种实现方式中,根据本公开的实施例的第一子模块231和第二子模块232的任一协作方式与第三子模块133和第四子模块134的任一协作方式可以自由组合,从而提供第一w参数和第二w参数。

下面结合图17描述根据本公开的实施例的如图16所示的电路400中包括扩展数据运算逻辑模块的部分的几种非限制性示例配置,其示出了第一子模块231和第二子模块232的协作方式与第三子模块133和第四子模块134的协作方式的非限制性示例组合。在图17中,以相邻两个运算级420-a和420-b为例进行说明,可以理解,在运算模块420中的任意相邻两个运算级都可以是以下讨论的运算级420-a和420-b。另外,在这些图中,为了清楚起见,用点线箭头指示直接移位而不经过运算的扩展数据的移动方向,用实线箭头指示经由第一子模块231和第二子模块232处理的扩展数据的移动方向,用点划线箭头指示经由第三子模块133和第四子模块134处理的扩展数据的移动方向,第一子模块至第四子模块的示意性框图在下方另行给出。

在如图17所示的示例中,运算级420-b的第一附加寄存器x1中的中间数据wx1′是通过由第一子模块231处理运算级420-a的第2扩展寄存器r2中存储的扩展数据w2、第3扩展寄存器r3中存储的扩展数据w3和第11扩展寄存器r11中存储的扩展数据w11得到的。具体地,在这个示例中,第一子模块231包括σ01运算器、全加器faa1和加法器add1,其中扩展数据w3被输入到σ01运算器,σ01运算器的输出、扩展数据w2和扩展数据w11被输入到全加器faa1,全加器faa1的输出被输入到加法器add1,加法器add1的输出被提供给运算级420-b的第一附加寄存器x1,使得wx1′=w2+σ0(w3)+w11。

进一步如图17所示,运算级420-b的第14扩展寄存器r14中的扩展数据w14′是通过由第二子模块232处理运算级220-a的第一附加寄存器x1中存储的中间数据wx1和运算级420-a的第14扩展寄存器r14中存储的扩展数据w14得到的。具体地,在这个示例中,第二子模块232包括σ11运算器和加法器add2,其中扩展数据w14被输入到σ11运算器,σ11运算器的输出和中间数据wx1被输入到加法器add2,加法器add2的输出被提供给运算级420-b的第14扩展寄存器r14,使得w14′=wx1+σ1(w14)。

进一步如图17所示,运算级420-b的第1扩展寄存器r1中的扩展数据w1′是通过由第三子模块133处理运算级420-a的第3扩展寄存器r3中存储的扩展数据w3、第4扩展寄存器r4中存储的扩展数据w4和第12扩展寄存器r12中存储的扩展数据w12得到的。具体地,在这个示例中,第三子模块133包括σ02运算器、全加器faa2和加法器add3,其中扩展数据w4被输入到σ02运算器,σ02运算器的输出、扩展数据w3和扩展数据w12被输入到全加器faa2,全加器faa2的输出被输入到加法器add3,加法器add3的输出被提供给运算级420-b的第1扩展寄存器r1,使得w1′=w3+σ0(w4)+w12。

进一步如图17所示,运算级420-b的第15扩展寄存器r15中的扩展数据w15′是通过由第四子模块134处理运算级420-a的第1扩展寄存器r1中存储的扩展数据w1和第15扩展寄存器r15中存储的扩展数据w15得到的。具体地,在这个示例中,第四子模块134包括σ12运算器和加法器add4,其中扩展数据w15被输入到σ12运算器,σ12运算器的输出和扩展数据w1被输入到加法器add4,加法器add4的输出被提供给运算级420-b的第15扩展寄存器r15,使得w15′=w1+σ1(w15)。

相应地,本公开也提供了在用于执行哈希算法的电路中计算扩展数据的方法。图21示出了根据本公开的实施例的在用于执行哈希算法的电路中计算扩展数据的方法800的示例性流程图。这样的电路可以包括被配置为接收数据的输入模块和被配置为基于接收到的数据计算哈希值的运算模块,其中运算模块可以包括以流水线结构布置的多个运算级,每个运算级包括第0扩展寄存器至第15扩展寄存器以及第一附加寄存器,每个扩展寄存器被配置为存储当前运算级的扩展数据,第一附加寄存器被配置为存储用于计算扩展数据的中间数据。对于运算模块的多个运算级中的包括第一运算级和在第一运算级之后的第二运算级的相邻两个运算级,方法800可以包括:在s801处,基于第一运算级的扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第一附加寄存器中的中间数据;在s802处,基于第一运算级的第一附加寄存器中存储的中间数据和第一运算级的第14扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第14扩展寄存器中的扩展数据;在s803处,基于第一运算级的第3扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第1扩展寄存器中的扩展数据;在s804处,基于第一运算级的第1扩展寄存器和第15扩展寄存器中存储的扩展数据计算用于存储到第二运算级的第15扩展寄存器中的扩展数据;在s805处,将第一运算级的第i扩展寄存器中存储的扩展数据作为用于存储到第二运算级的第(i-2)扩展寄存器中的扩展数据,其中4≤i≤15且i为整数,并且将第一运算级的第2扩展寄存器中存储的扩展数据作为用于存储到第二运算级的第0扩展寄存器中的扩展数据,其中4≤i≤15且i为整数。注意,s801-s805并不需要以顺序次序执行,而是可以以任何次序执行,或者可以至少部分地并行执行。

说明书及权利要求中的词语″左″、″右″、″前″、″后″、″顶″、″底″、″上″、″下″、″高″、″低″等,如果存在的话,用于描述性的目的而并不一定用于描述不变的相对位置。应当理解,这样使用的词语在适当的情况下是可互换的,使得在此所描述的本公开的实施例,例如,能够在与在此所示出的或另外描述的那些取向不同的其它取向上操作。例如,在附图中的装置倒转时,原先描述为在其它特征″之上″的特征,此时可以描述为在其它特征″之下″。装置还可以以其它方式定向(旋转90度或在其它方位),此时将相应地解释相对空间关系。

在说明书及权利要求中,称一个元件位于另一元件″之上″、″附接″至另一元件、″连接″至另一元件、″耦合″至另一元件、或″接触″另一元件等时,该元件可以直接位于另一元件之上、直接附接至另一元件、直接连接至另一元件、直接耦合至另一元件或直接接触另一元件,或者可以存在一个或多个中间元件。相对照的是,称一个元件″直接″位于另一元件″之上″、″直接附接″至另一元件、″直接连接″至另一元件、″直接耦合″至另一元件或″直接接触″另一元件时,将不存在中间元件。在说明书及权利要求中,一个特征布置成与另一特征″相邻″,可以指一个特征具有与相邻特征重叠的部分或者位于相邻特征上方或下方的部分。

如在此所使用的,词语″示例性的″意指″用作示例、实例或说明″,而不是作为将被精确复制的″模型″。在此示例性描述的任意实现方式并不一定要被解释为比其它实现方式优选的或有利的。而且,本公开不受在技术领域、背景技术、实用新型内容或具体实施方式中所给出的任何所表述的或所暗示的理论所限定。如在此所使用的,词语″基本上″意指包含由设计或制造的缺陷、器件或元件的容差、环境影响和/或其它因素所致的任意微小的变化。词语″基本上″还允许由寄生效应、噪声以及可能存在于实际的实现方式中的其它实际考虑因素所致的与完美的或理想的情形之间的差异。

另外,仅仅为了参考的目的,还可以在本文中使用″第一″、″第二″等类似术语,并且因而并非意图限定。例如,除非上下文明确指出,否则涉及结构或元件的词语″第一″、″第二″和其它此类数字词语并没有暗示顺序或次序。还应理解,″包括/包含″一词在本文中使用时,说明存在所指出的特征、整体、步骤、操作、单元和/或组件,但是并不排除存在或增加一个或多个其它特征、整体、步骤、操作、单元和/或组件以及/或者它们的组合。在本公开中,术语″提供″从广义上用于涵盖获得对象的所有方式,因此″提供某对象″包括但不限于″购买″、″制备/制造″、″布置/设置″、″安装/装配″、和/或″订购″对象等。

本领域技术人员应当意识到,在上述操作之间的边界仅仅是说明性的。多个操作可以结合成单个操作,单个操作可以分布于附加的操作中,并且操作可以在时间上至少部分重叠地执行。而且,另选的实施例可以包括特定操作的多个实例,并且在其它各种实施例中可以改变操作顺序。但是,其它的修改、变化和替换同样是可能的。可以以任何方式和/或与其它实施例的方面或元件相结合地组合以上公开的所有实施例的方面和元件,以提供多个附加实施例。因此,本说明书和附图应当被看作是说明性的,而非限制性的。